Integrované obvody jsou vícevrstvé struktury, jejichž klíčovými prvky jsou vícehradlové (multi-gate) tranzistory, kde je vodivý kanál (fin) mezi emitorem a kolektorem obklopen 3D hradlem.

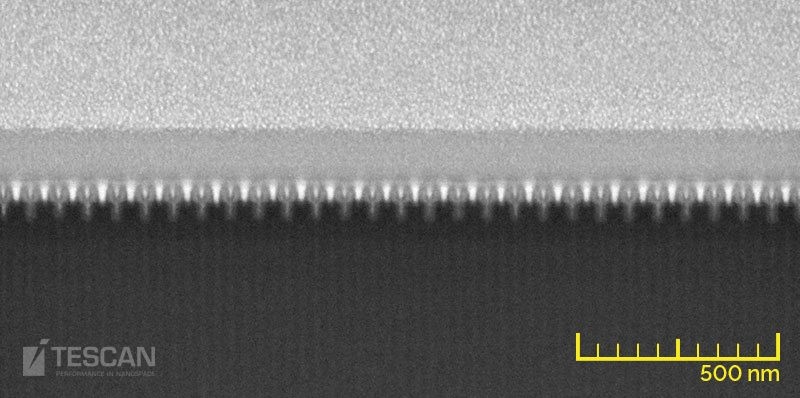

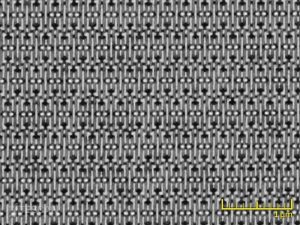

Intel procesor vyrobený technologií 14 nm. Vrchní pohled na kontaktní vrstvu tranzistoru po delayeringu, provedeného pomocí GIS asistovaného leptání Xe Plasma FIBem, obraz získaný při elektronovém urychlujícím napětí 500 V pomocí detektoru In-Beam.

- Analýza poruch integrovaných obvodů obvykle zahrnuje delayering a elektrickou lokalizaci defektu. Pro identifikaci příčiny defektu lze připravit lamelu pro kontrolu na transmisním elektronovém mikroskopu (TEM).

- Dříve se delayering prováděl zejména mechanickým obrušováním. Tato metoda však dosáhla svých technologických limitů a při dnešních velikostech polovodičů ji často již nelze použít kvůli mikro- a nanomechanické deformaci a také chemickým interakcím s lešticí suspenzí.

- Přípravu TEM lamely je možné realizovat na systémech FIB-SEM, kde je možné dosáhnout lamel bez nežádoucích artefaktů s tloušťkou odpovídající současným potřebám polovodičového průmyslu.

Analýza chyb v integrovaných obvodech obvykle zahrnuje:

- Delayering a elektrickou analýzu (I-V charakteristika)

- Přípravu TEM lamely z integrovaných obvodů

- FIB-SEM tomografii pro 3D strukturální analýzu (3D rekonstrukce BSE)

- Elektrickou poruchovou lokalizaci (EBIC, EBAC)

- Nízkoenergiovou inspekci pomocí SEM

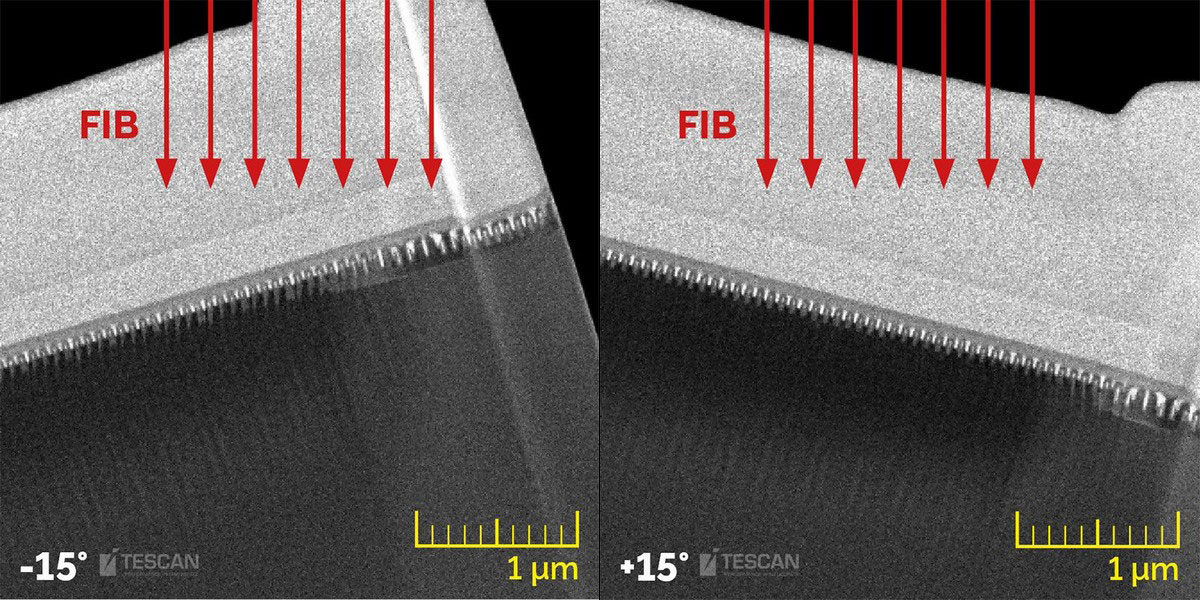

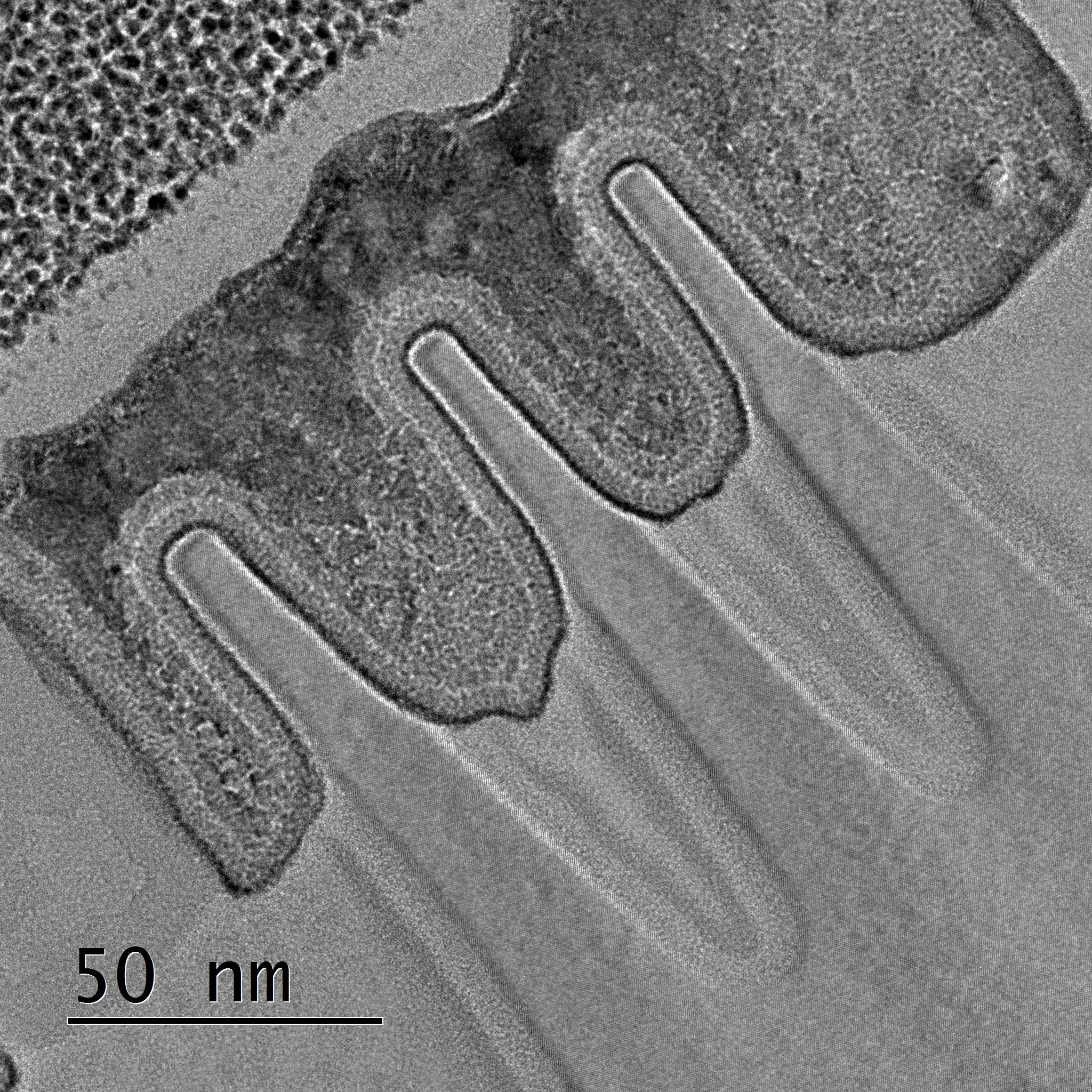

- 14 nm procesor Intel. Náklon základny pomáhá zmírňovat artefakty během výroby TEM lamely postupnými náklony vzorku do +/− 15° při ztenčování lamely.

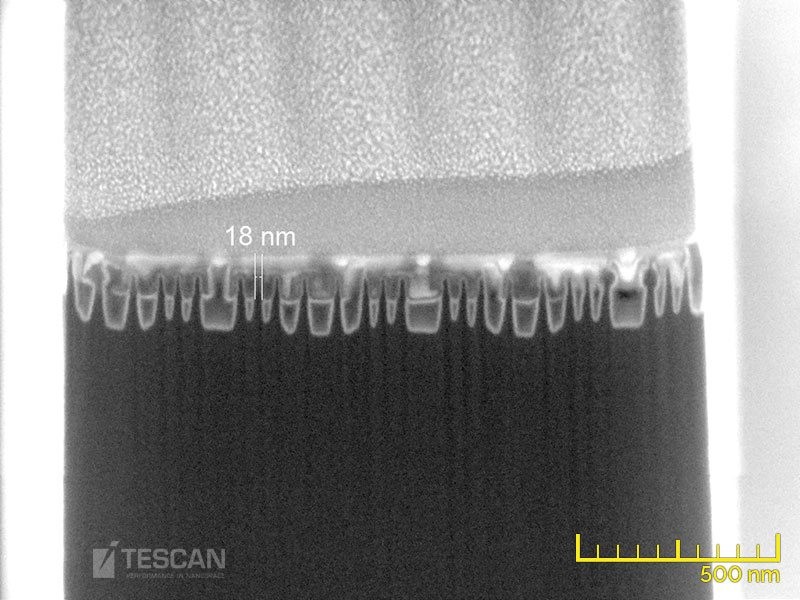

- 14 nm procesor Intel. Boční pohled: řez příčně vodivým kanálem lamely během ztenčování, konečná lamela byla připravena právě uprostřed jednoho žebra substrátu (její tloušťka je menší než 20 nm).

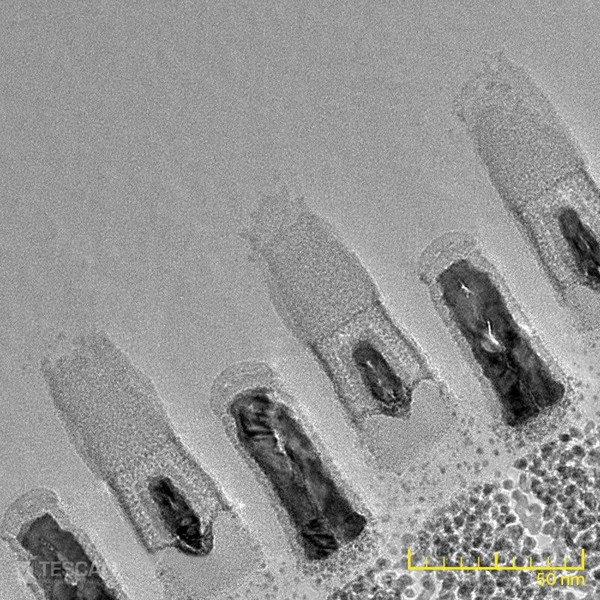

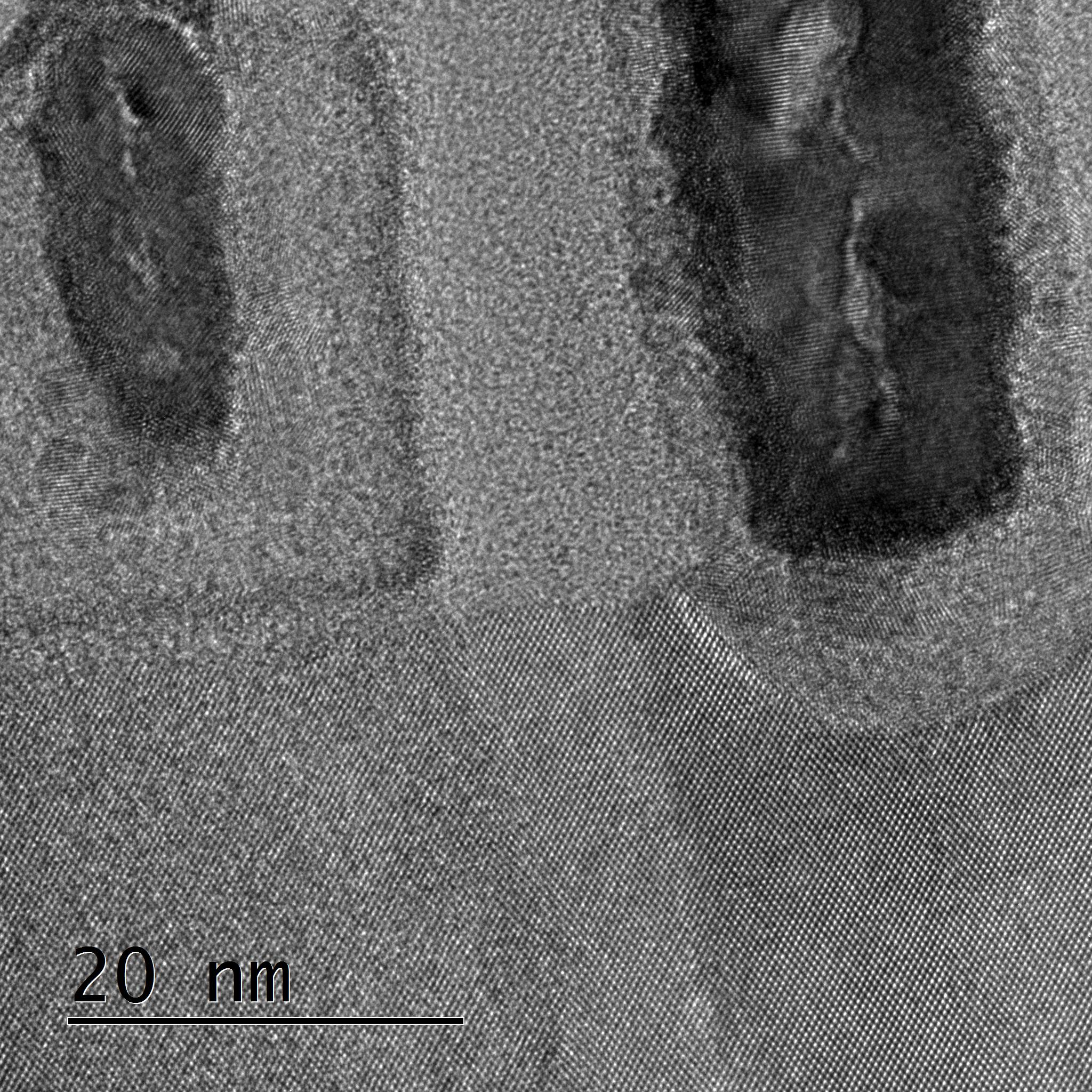

- TEM obraz s vysokým rozlišením, lamela v řezu s hradlovou vrstvou z čipu o velikosti 14 nm, připravená pomocí invertovaného ztenčování.

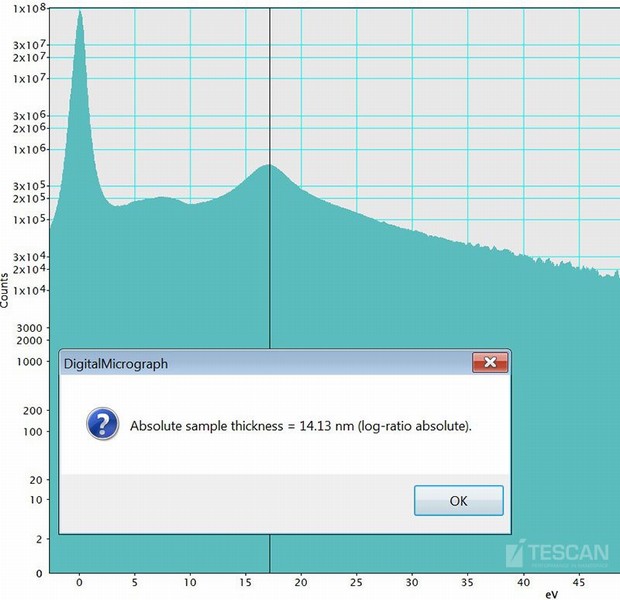

- 14 nm procesor Intel. Spektrum EELS potvrdilo, že tloušťka lamely je pod 15 nm.

- 14 nm procesor Intel. Průřez znázorňující tranzistorové vrstvy („Gate-cut“) a zobrazený při napětí 5 kV detektorem In-Beam.

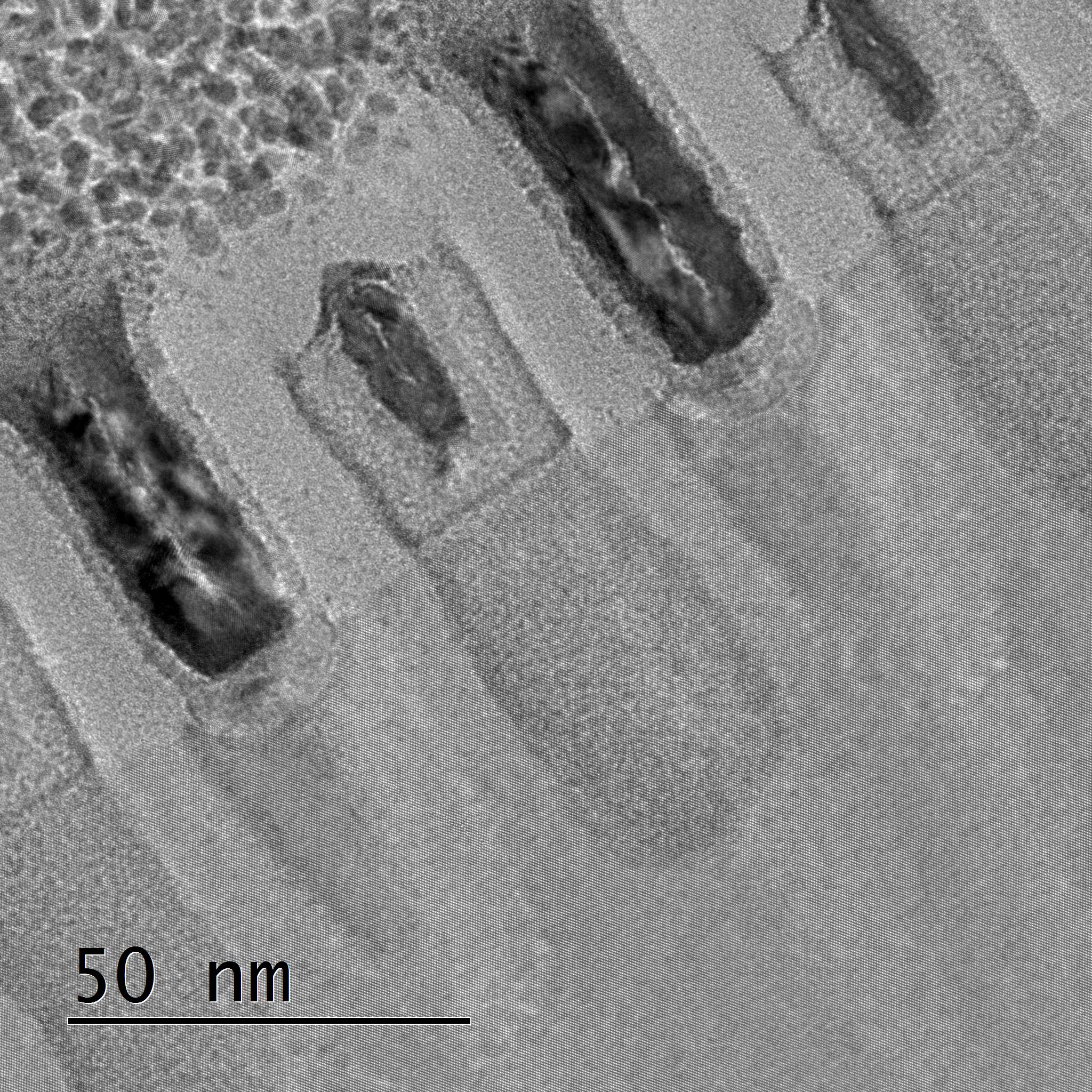

- TEM snímek s vysokým rozlišením: lamela připravená z čipu o velikosti 14 nm pomocí ztenčování shora dolů.

- TEM obraz lamely, připravené z čipu o velikosti 14 nm pomocí ztenčování shora dolů s použitím naklápěcího stolku.

- TEM obraz lamely, připravené z čipu o velikosti 14 nm pomocí ztenčování shora dolů s použitím naklápěcího stolku.